Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Special AMD Ryzen 9 7950X3D im Test: Der Gipfel der CPU-Entwicklung

- Ersteller PCGH-Redaktion

- Erstellt am

@Nathenhale

Ja und smt bzw ht teilen sich zudem auch noch den l1 und l2. Heißt wenn nur 1 Kern nur 1 thread ausgelastet ist, kann dann der Kern über die ganze Cache verfügen oder geht der Teil wo ht und smt gebraucht haben auch noch weg?

Also sprich bei 1024 müsste es ja dann 512 für 1 Kern und 512 kb für die smt bzw ht sein. Oder spielt dies keine Rolle weil wenn eines nicht nutzt es der Andere Teil des Kernes es voll nutzen kann?

Spielt keine Rolle, der Cache wird gemeinsam genutzt. Sonst hätte SMT massive Nachteile, die nicht aufzuholen wären.

Das ist ja auch dann der Witz eines großen L3 Cache, der allen Kernen zu gute kommt.

G

Gelöschtes Mitglied 217606

Guest

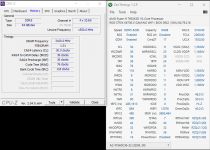

Danke! Wow, hätte nicht gedacht, dass ein Asus Board solche gcrippelten Settings verwendet.Hier, aber ich hatte noch keine Zeit für nen großartigen Feinschliff.

1/2 UCLK kostet ordentlich Performance.

@openSUSE

OK das gillt also sowohl als auch für den l1, l2 und l3 cache.Spielt keine Rolle, der Cache wird gemeinsam genutzt. Sonst hätte SMT massive Nachteile, die nicht aufzuholen wären.

Das erklärt auch warum die latenz beim Cache so wichtig ist. Weil wenn alle Kerne gleichzeitig gut ausgelastet sind dann kann es schon mal zu Engpass kommen. Weil genau für pro Kern cache 2 zugriffe gleichzeitig stattfinden. Ich wusste nicht das es da dann nicht zu einen Engpass oder sogar zum Überlauf beim Zugriff kommen wird. Warum weil 2 Sachen Kern mit smt gleichzeitig den Cache drauf zugreifen und so ne höhere Belastung beim beim cach statt findet.

Das kann dann auch auf die Leistung drücken. Und was sagt die Anzahl der threads die man ja selbst einstellen kann oder durch automatischen Einstellung dann wo es so anbietet über die Leistung aus?

Und ich weiß je mehr thread ne Anwendung braucht was sagt es dann über den Cache und so aus und deren Belastung.

Wollte ja wissen wie viel Cache die die jeweilige Anwendung insgesammt braucht sowie auch wie sich die Fehler auswirkt. Oder gehe ich da schon viel zu tief in die CPU ein im Gegensatz zu anderen Menschen hier?

Ishe

PC-Selbstbauer(in)

Danke! Wow, hätte nicht gedacht, dass ein Asus Board solche gcrippelten Settings verwendet.

1/2 UCLK kostet ordentlich Performance.

@openSUSE

Speicher kommt am WE dran, null Zeit im Moment. Nur zusammengeschraubt und nun erstmal fertig installieren.

Eben nur nen ASUS preset geladen.

Anhänge

Falls das Regal da rechts im Bild mal aus allen Nähten platzt (und danach sieht es fast schon aus), bin ich euch gerne beim einlagern behilflich @PCGH_Dave

Gibts mehr Geld.Nachtschicht incoming?

Bei Computec?mehr Geld

Erzähl mir mehr, dann versuche ich vlt. einen Neustart

Zwischen jetzt und morgen Früh liegen noch knapp 12h...

15 Uhr wäre mir lieber, dann kann ich nach der Arbeit direkt live einsteigen ^^

WTF?

Ist es schon morgen früh?

www.pcgameshardware.de

www.pcgameshardware.de

Ist es schon morgen früh?

AMD Ryzen 9 7900X3D im Benchmark-Test: Sind sechs Kerne die Macht?

Im Schatten des großen 16-Kerners hat auch der 12-Kerner Ryzen 9 7900X3D mit zwei Sechskern-CCDs das Licht der Welt erblickt. PCGH hat den Test gemacht.

0ldN3rd

BIOS-Overclocker(in)

....wie die Zeit vergeht.....WTF?

Ist es schon morgen früh?

AMD Ryzen 9 7900X3D im Benchmark-Test: Sind sechs Kerne die Macht?

Im Schatten des großen 16-Kerners hat auch der 12-Kerner Ryzen 9 7900X3D mit zwei Sechskern-CCDs das Licht der Welt erblickt. PCGH hat den Test gemacht.www.pcgameshardware.de

Joa, @PCGH_Thilo hat das jetzt entschieden, ich hatte auch alle Rohre für morgen früh klargemacht

Jetzt ist es halt so, freut euch doch, dann könnt ihr das Dinge heute schon bestaunen

Jetzt ist es halt so, freut euch doch, dann könnt ihr das Dinge heute schon bestaunen

Generell Nachtschicht zumindest hier in Österreich und zwar Signifikant mehr. Egal welcher Job.Bei Computec?

Erzähl mir mehr, dann versuche ich vlt. einen Neustartim Auslandin Bayern.

Redaktionen, nicht nur bei Computec, funktionieren in der Regel nicht mit festen Schichten, die gezielt entlohnt werden könnten, sondern arbeiten mit flexibler Vertrauensarbeitszeit.

(Der Chef vertraut darauf, dass die Redakteure einen Weg finden, alles fertig zu stellen.^^)

(Der Chef vertraut darauf, dass die Redakteure einen Weg finden, alles fertig zu stellen.^^)

Das funktioniert anscheinend ähnlich wie im Einzelhandel

CD LABS: Radon Project

Lötkolbengott/-göttin

Und es wird Zeit, dass sich daran etwas ändert. Kein aktuelles System sollte Leistungsaufnahmen im zweistelligen Wattbereich aufweisen; weder bei Intel noch bei AMD.Hab ich mir gedacht - also an der Stelle unverändert zu den Vorgängern.

Und gerade Chipletdesigns sollten nicht schwach, sondern besonders stark aufgestellt sein. Schließlich gäbe es dort die Möglichkeit, einen Teilbereich komplett zu deaktivieren!

Ähnliche Themen

- Antworten

- 61

- Aufrufe

- 5K

- Antworten

- 19

- Aufrufe

- 1K

- Antworten

- 28

- Aufrufe

- 2K

- Antworten

- 54

- Aufrufe

- 3K

- Antworten

- 54

- Aufrufe

- 4K

ich bin dann mal wech vom Fenster, für heute habe ich die Nase voll

ich bin dann mal wech vom Fenster, für heute habe ich die Nase voll  , viel Spaß beim Lesen morgen, gibt ein paar Überraschungen, kann ich schon sagen.

, viel Spaß beim Lesen morgen, gibt ein paar Überraschungen, kann ich schon sagen.